数字电子技术基础 时序逻辑电路的设计方法与有限状态机在集成电路设计中的应用

在数字电子技术的领域中,时序逻辑电路是实现复杂数字系统功能的核心。其设计与分析构成了现代集成电路,特别是数字信号处理、控制器和微处理器的基础。本节将重点探讨时序逻辑电路的设计方法,并深入解析有限状态机(FSM)这一关键设计范式及其在集成电路设计中的实践应用。

一、时序逻辑电路设计方法概述

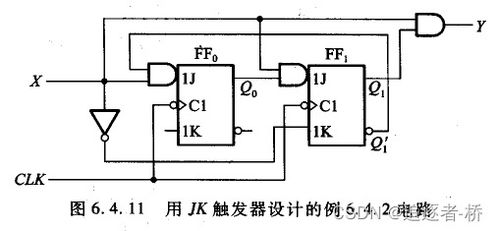

时序逻辑电路与组合逻辑电路的根本区别在于其输出不仅取决于当前的输入,还与电路过去的状态(即历史输入序列)有关。这个“过去的状态”由电路内部的存储元件(主要是触发器,如D触发器、JK触发器等)来记忆。因此,时序逻辑电路的设计核心在于:如何根据给定的逻辑功能要求,系统地确定所需触发器的数量、类型,并推导出驱动这些触发器的组合逻辑(即激励方程)以及电路的输出方程。

经典的设计流程通常包括以下几个步骤:

- 逻辑抽象,建立原始状态图/表:将文字描述的设计要求转化为用状态(如S0, S1, S2...)和状态转换关系表示的图形或表格。这是最关键也是最需要创造性的步骤。

- 状态化简:消除原始状态图中的冗余状态,以最简的状态数实现所需功能,从而降低电路复杂度。

- 状态分配(状态编码):为化简后的每个状态分配一个唯一的二进制代码。不同的编码方案会影响后续组合电路的复杂度和电路的性能(如速度、功耗)。

- 选择触发器类型:根据设计需求(如速度、面积、功耗)和熟悉程度,确定使用D、T、JK等触发器中的哪一种。

- 推导输出方程和激励方程:根据状态转换关系和所选触发器的特性表/特性方程,利用卡诺图或布尔代数等工具,求出驱动各触发器输入的组合逻辑表达式(激励方程)以及电路的输出逻辑表达式(输出方程)。

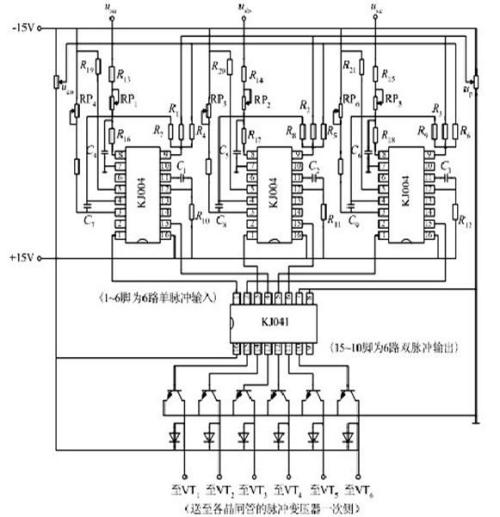

- 画逻辑电路图:根据求得的方程,用逻辑门和触发器画出完整的电路图。

- 验证与检查:通过仿真或理论分析,检查电路功能是否满足原始要求,是否存在竞争-冒险等隐患。

二、有限状态机(FSM)的核心地位

在时序逻辑电路设计中,有限状态机(Finite State Machine, FSM) 是一个极其强大且通用的理论模型和设计工具。它将一个系统抽象为有限数量的状态,以及在输入信号触发下,从一个状态迁移到另一个状态的规则。

FSM主要分为两类:

- 摩尔型(Moore Machine):输出仅由当前状态决定。其输出与时钟同步,稳定性好,但响应输入变化会延迟一个时钟周期。

- 米利型(Mealy Machine):输出由当前状态和当前输入共同决定。它能更快地对输入变化作出响应,但输出可能出现毛刺,且可能异步于时钟。

在设计中采用FSM模型,具有以下优势:

- 思维结构化:将复杂的行为分解为清晰的状态和转换,使设计思路条理化。

- 可描述性强:非常适合于描述具有顺序或事件驱动特性的控制逻辑,如交通灯控制器、通信协议解析器、游戏逻辑等。

- 易于实现与验证:其数学模型清晰,可以方便地使用硬件描述语言(如VHDL、Verilog)进行描述,并利用EDA工具进行综合、仿真和验证。

三、FSM在集成电路设计中的实践

在现代超大规模集成电路(VLSI)和片上系统(SoC)设计中,FSM的应用无处不在。设计流程已高度依赖于电子设计自动化(EDA)工具。

- 高层次建模:设计师首先使用硬件描述语言(HDL)以行为级或RTL(寄存器传输级)方式描述FSM。例如,在Verilog中,通常使用

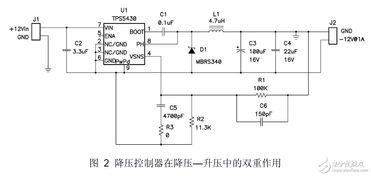

always块和case语句来清晰地表达状态寄存器的更新和输出逻辑。 - 逻辑综合:EDA工具读取HDL代码,根据目标工艺库(如某家半导体公司的标准单元库)的约束,自动将FSM描述“综合”成由基本逻辑门和触发器构成的门级网表。工具会自动完成状态编码优化(如One-hot编码、格雷码等)、逻辑最小化等工作。

- 验证与仿真:在设计前后,通过功能仿真、时序仿真等形式,确保FSM在各种输入序列下都能正确工作,并满足建立时间、保持时间等时序要求。

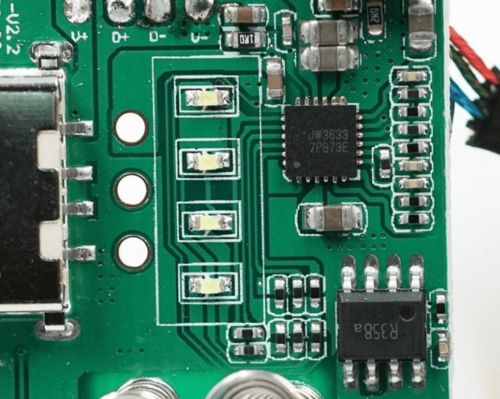

- 物理实现:综合后的网表经过布局布线,生成最终的芯片版图。FSM作为控制模块,通常与数据通路模块紧密集成,共同完成复杂功能。

四、

时序逻辑电路的设计,尤其是基于有限状态机的设计方法,是连接数字系统抽象功能与具体硬件实现的桥梁。掌握从问题抽象到状态图建立,再到最终电路实现或HDL编码的完整流程,是数字电子技术工程师和集成电路设计师的核心能力。随着EDA技术的发展,设计的抽象层次不断提高,但FSM的基本思想和设计原则依然是理解、分析和构建任何复杂数字控制系统的坚实基础。从简单的计数器、序列检测器到复杂的CPU指令控制器,FSM的身影贯穿始终,彰显了其在数字世界设计中的永恒生命力。

如若转载,请注明出处:http://www.siliao100.com/product/5.html

更新时间:2026-04-22 18:34:24