以太网保护电路设计 集成电路设计中的关键考量与前沿策略

以太网作为现代通信网络的核心技术,其物理接口(PHY)及外围电路在各种复杂环境中面临着严峻的电气威胁,如静电放电(ESD)、电气快速瞬变(EFT)、浪涌(Surge)及电缆放电事件(CDE)等。因此,稳健可靠的以太网保护电路设计,特别是其与集成电路(IC)的协同设计,已成为保障网络设备高可用性与长寿命的关键环节。本文将深入探讨以太网保护电路的设计原理、集成电路层面的集成策略以及前沿发展趋势。

一、 以太网接口面临的主要威胁与保护标准

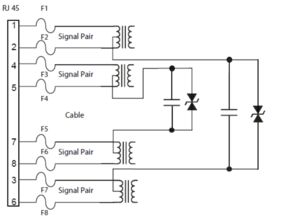

以太网接口,尤其是通过双绞线(如CAT5e/6)连接的RJ-45端口,暴露在外,易受以下干扰:

1. 静电放电(ESD): 人体或设备带电对端口的直接放电,遵循IEC 61000-4-2标准,要求承受高达±8kV(接触)或±15kV(空气)的冲击。

2. 浪涌(Surge): 由雷电感应或大型设备开关引起的瞬时高压大电流,遵循IEC 61000-4-5标准,常见测试等级为线-地±1kV/2kV,线-线±0.5kV/1kV。

3. 电气快速瞬变(EFT): 继电器、开关触点抖动产生的一系列快速脉冲群,遵循IEC 61000-4-4标准。

这些威胁若不加以抑制,会直接损坏PHY芯片内部的精密晶体管,导致通信中断或永久性故障。

二、 传统分立式保护电路设计

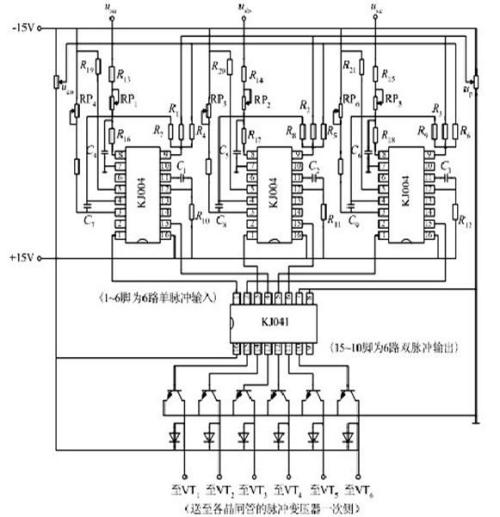

在PHY芯片外部,通常采用分立保护器件构建第一道防线:

- 瞬态电压抑制器(TVS)二极管阵列: 这是最核心的保护元件。针对以太网差分线对(TX±, RX±),需选用低钳位电压、低寄生电容(通常<5pF,以保持信号完整性,尤其是千兆及以上速率)的专用TVS阵列。它们被并联在信号线与地之间,当电压超过击穿值时迅速导通,将过压能量泄放到地。

- 共模扼流圈(CMC): 放置于TVS之前,用于抑制共模噪声,增强电磁兼容性(EMC),同时也能减缓部分瞬态干扰的上升沿。

- 隔离变压器: 这是以太网接口的标配,提供电气隔离、阻抗匹配和信号耦合。其绕组间的隔离电压是系统绝缘能力的重要部分。保护电路通常布置在变压器(靠近RJ-45侧)和PHY芯片之间。

三、 集成电路设计中的保护集成策略

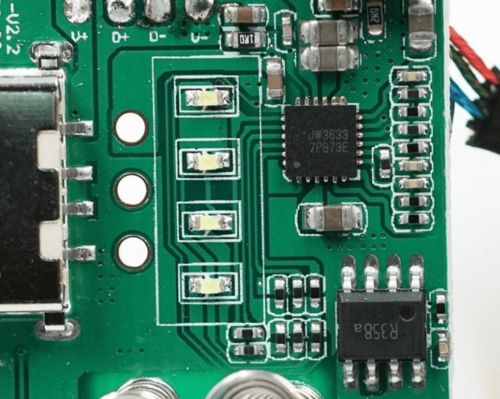

随着工艺进步和系统小型化需求,将部分或全部保护功能集成到PHY芯片内部成为重要趋势,这对IC设计提出了更高要求:

- 片上ESD保护结构: 在PHY芯片的每个I/O焊盘上,都必须设计有标准的ESD保护单元(如基于GGNMOS、SCR器件的钳位电路),以应对芯片制造、封装、测试和组装过程中的ESD事件。这些结构需要与高速收发电路的性能进行精密的协同优化(Area-Performance-Reliability Trade-off)。

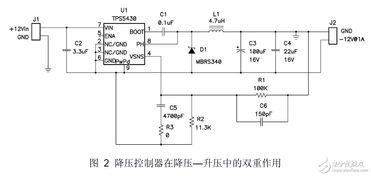

- 增强型片上浪涌保护: 集成能够承受更高能量(如±1kV Surge)的片上保护电路是前沿挑战。这通常需要:

- 采用特殊工艺与器件: 如深阱工艺、高压器件,设计大尺寸的箝位器件以分散能量。

- 智能主动保护电路: 集成检测电路,当侦测到浪涌事件时,快速开启大尺寸箝位晶体管,并在事件结束后关闭,避免影响正常信号。

- 与封装及PCB协同设计: 利用芯片封装引脚和PCB走线的电感/电阻作为限流元件,与片上保护结构共同作用。

- 系统级芯片(SoC)的协同考虑: 在集成PHY的复杂SoC中,需要从系统级进行电源域隔离、衬底噪声隔离,防止瞬态干扰通过电源网络或衬底耦合到其他敏感模块(如处理器核心)。

四、 混合保护方案与设计权衡

最优设计往往是分立与集成保护的混合方案:

- 分层保护架构: 第一级(靠近接口)采用分立高性能TVS,用于吸收大部分能量;第二级为片上保护,处理残压和更快的ESD事件。这种架构提供了最佳的可靠性与成本平衡。

- 关键设计权衡:

- 性能 vs. 保护水平: 集成保护器件引入的寄生电容会影响信号边沿,限制最高传输速率。设计必须在保护能力和带宽之间取得平衡。

- 成本 vs. 集成度: 全集成方案节省PCB空间和BOM成本,但可能增加芯片面积、工艺复杂度和研发风险。

- 标准符合性 vs. 实际应用场景: 设计需满足相关行业标准(如IEEE 802.3, IEC),并针对设备部署环境(如户外、工业环境)进行强化。

五、 未来发展趋势

- 更先进的工艺与器件: 基于GaN、SiC等宽禁带半导体的保护器件有望提供更低的电容和更快的响应。

- 智能化与可重构保护: 集成传感器和数字控制逻辑,实现保护阈值的动态调整和故障自诊断。

- 针对更高速度的优化: 随着2.5G/5G/10G BASE-T乃至更高速率以太网的普及,对保护电路带宽和信号完整性的要求将愈发严苛,推动着保护设计与信号路径的共仿真与一体化设计。

结论

以太网保护电路设计是一个多学科交叉的领域,涉及电磁学、半导体物理、电路设计和系统架构。在集成电路设计层面,它不再仅仅是I/O焊盘上的附加单元,而是需要与高速收发机、电源管理、物理布局进行深度协同的核心可靠性设计。未来的发展方向将是更高度的集成、更智能的响应以及在极端电气环境下无懈可击的稳健性,为万物互联的可靠通信奠定坚实基础。

如若转载,请注明出处:http://www.siliao100.com/product/7.html

更新时间:2026-04-22 23:04:49